AD1862 blir av av en håndfull kyndige mennesker regnet som den ultimate R-2R dacen. Det er en mono chip med +-12V forsyningsspenning og Iout. Den ble aldri tatt i bruk kommersielt i noen særlig stor skala, og er for lengst gått ut av produksjon, men er fortsatt mulig å oppdrive.

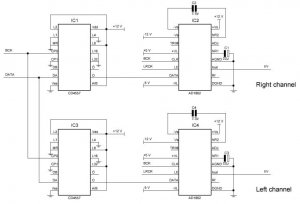

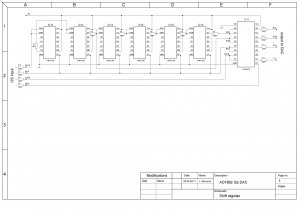

Så til poenget... jeg fikk en litt sprø idé om å forsøke å lage en dac fra scratch, basert på denne chipen. Planen var å kjøre USB til I2S, deretter til et digitalt filter og videre til dac. For å gjøre det litt enklere tenkte jeg å basere meg på ferdige moduler for USB-receiver og digitalt filter.

Audio-GD leverer digitale filtermoduler basert på Altera Cyclone II, som gir MSB-first ut:

http://www.audio-gd.com/Pro/dac/DSP1/DSP1ENspecs.htm

pcm63.com leverer NOS AD1862-chiper:

http://pcm63.com/?69,ad1862n-j-military

Jeg har lite erfaring med digital kretsdesign, så det ville blitt et forskningsprosjekt med bratt læringskurve. Er det noen som har erfaring med denne typen dacer? Noen som kan si om dette er et prosjekt som kan la seg gjennomføre? Jeg tar imot innspill med åpne armer.

Så til poenget... jeg fikk en litt sprø idé om å forsøke å lage en dac fra scratch, basert på denne chipen. Planen var å kjøre USB til I2S, deretter til et digitalt filter og videre til dac. For å gjøre det litt enklere tenkte jeg å basere meg på ferdige moduler for USB-receiver og digitalt filter.

Audio-GD leverer digitale filtermoduler basert på Altera Cyclone II, som gir MSB-first ut:

http://www.audio-gd.com/Pro/dac/DSP1/DSP1ENspecs.htm

pcm63.com leverer NOS AD1862-chiper:

http://pcm63.com/?69,ad1862n-j-military

Jeg har lite erfaring med digital kretsdesign, så det ville blitt et forskningsprosjekt med bratt læringskurve. Er det noen som har erfaring med denne typen dacer? Noen som kan si om dette er et prosjekt som kan la seg gjennomføre? Jeg tar imot innspill med åpne armer.